Smart Electronics Beaglebone BB Black Embedded Development Board AM3358 Motherboard Linux Single-Board ARM Computer

Smart Electronics Beaglebone BB Black Embedded Development Board AM3358 Motherboard Linux Single-Board ARM Computer

Product Overview

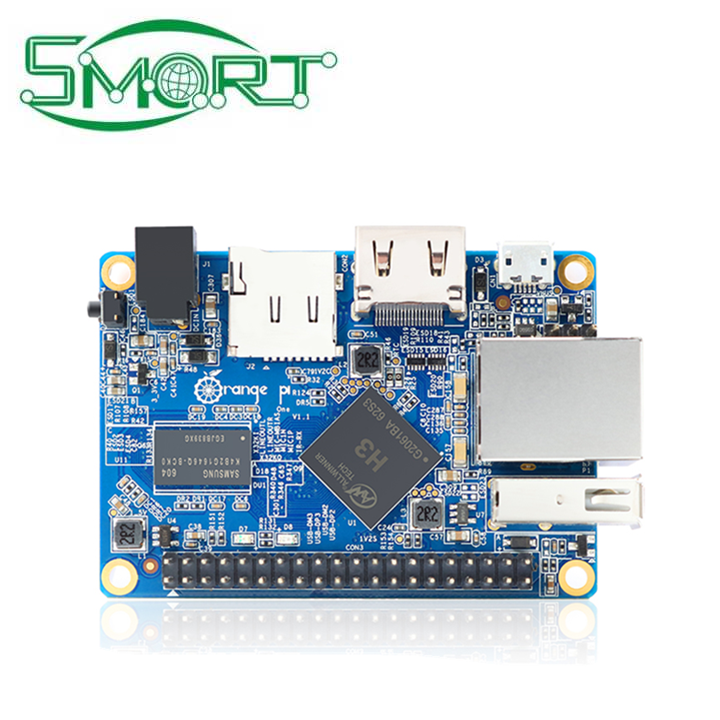

BB Black is a development kit based on the AM335x processor. The processor integrates an ARM

Cortex-A8 core and provides a rich array of peripheral interfaces. The Chinese version of BB-Black

features expansion interfaces including Ethernet, USB Host, USB OTG, TF card slot, serial port, JTAG

interface (unpopulated by default), HDMI Type interface, eMMC, ADC, I2C, SPI, PWM, and LCD display interface.

The Chinese version of BB-Black serves a wide range of applications, meeting diverse needs across

various fields including gaming peripherals, home and industrial automation, consumer medical devices,

printers, smart payment systems, smart vending machine weighing systems, educational terminals,

and advanced toys. General-purpose interfaces include 4 sets of General-Purpose Input/Output (GPIO) modules,

each providing 32 dedicated GPIO pins. Thus, the total number of GPIO pins can reach up to 128 (4x32).

The Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS) incorporates

two 32-bit RISC cores (Programmable Real-Time Units, or PRUs), memory, terminal controllers,

and internal peripherals supporting additional interfaces and protocols.

The POWERVR® SGX graphics accelerator subsystem enables 3D graphics acceleration for display and gaming effects.

Key features include:

· Tile-based architecture with processing power up to 20 million operations per second

· Universal scalable rendering engine: a multithreaded engine with pixel and vertex rendering capabilities

· Advanced rendering instruction set exceeding Microsoft VS 3.0, PS 3.0, and OGL 2.0

· Industry-standard APIs supporting Direct3D Mobile, OGL-ES 1.1 and 2.0, OpenVG 1.0, and OpenMAX

Product Specifications

Product Dimensions: 86.36 mm x 54.61 mm

Ambient Humidity: 20% to 90% (non-condensing)

Operating Temperature: 0°C to 70°C

Input Power: 5V/0.35A

AM335x Processor

Integrated 1 GHz ARM Cortex-A8 core

Integrated NEON SIMD coprocessor

Integrated SGX530 graphics engine

Integrated programmable real-time unit subsystem

Integrated 32KB instruction cache and 32KB data cache with parity support

Integrated 256KB L2 cache with error-correcting code support